intel Agilex loginio masyvo blokai ir adaptyvieji logikos moduliai

Intel® Agilex™ LAB ir ALM Overview

Loginis masyvo blokas (LAB) sudarytas iš pagrindinių kūrimo blokų, žinomų kaip adaptyvieji logikos moduliai (ALM). Galite sukonfigūruoti LAB įgyvendinti logines, aritmetines ir registro funkcijas.

Pusę galimų LAB „Intel® Agilex™“ įrenginiuose galite naudoti kaip atminties LAB (MLAB). Tam tikri įrenginiai gali turėti didesnį MLAB koeficientą.

„Intel Quartus® Prime“ programinė įranga ir kiti palaikomi trečiųjų šalių sintezės įrankiai automatiškai parenka tinkamą režimą įprastoms funkcijoms, tokioms kaip skaitikliai, sumatoriai, atimtuvai ir aritmetinės funkcijos.

„Intel Hyperflex™ Core Architecture“, „Intel Agilex Device Over“.view

Pateikiama daugiau informacijos apie „Hyper-Registers“ ir „Intel Hyperflex™“ pagrindinę architektūrą. „Hyper-Registers“ yra papildomi registrai, prieinami kiekviename sujungimo maršruto segmente visame pagrindiniame audinyje, įskaitant maršruto parinkimo segmentus, prijungtus prie LAB įėjimų ir išėjimų.

„Intel Hyperflex™“ registras

„Intel Agilex“ įrenginių šeima yra pagrįsta „Intel Hyperflex™“ pagrindine architektūra.

„Intel Agilex LAB“ yra „Intel Hyperflex“ registrai ir kitos funkcijos, skirtos palengvinti pakartotinį nustatymą. „Intel Hyperflex“ registrai yra ALM ir nešiojimo grandinėse. Kaip parodyta paveikslėlyje „Intel Agilex ALM Connection Details“, „Intel Hyperflex“ registrai yra ant sinchroninio išvalymo, o laikrodžio įėjimai leidžia padidinti arba sumažinti kelio delsą. Visus „Intel Hyperflex“ registrus galima įjungti ir juos valdo „Intel Quartus Prime“ programinė įranga per atstatymą.

Intel Agilex LAB ir ALM architektūra ir funkcijos

Tolesniuose skyriuose aprašomos „Intel Agilex“ įrenginių LAB ir ALM.

LAB

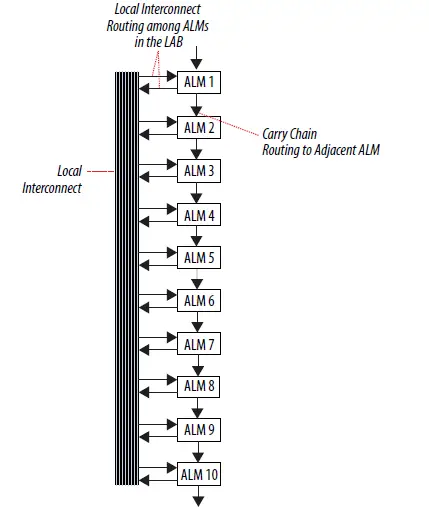

LAB yra konfigūruojami loginiai blokai, susidedantys iš loginių išteklių grupės. Kiekvienoje LAB yra speciali logika, skirta valdymo signalams nukreipti į savo ALM. MLAB yra LAB superrinkinys ir apima visas LAB funkcijas. Kiekvienoje LAB iš viso yra 10 ALM, kaip parodyta Intel Agilex LAB ir MLAB struktūros paveiksle.

1 pav.

„Intel Agilex LAB“ struktūra ir jungtysview

Šis paveikslėlis rodo perėjimąview Intel Agilex LAB ir MLAB struktūros su LAB jungtimis.

Susijusi informacija

Susijusi informacija

MLAB 6 puslapyje

MLAB

Kiekvienas MLAB palaiko daugiausia 640 bitų paprastos dviejų prievadų SRAM. Galite sukonfigūruoti kiekvieną MLAB ALM kaip 32 (gylis) x 2 (plotis) atminties bloką, todėl konfigūracija yra 32 (gylis) x 20 (plotis) paprastas dviejų prievadų SRAM blokas.

2 pav.

Intel Agilex LAB ir MLAB struktūra Vietinis ir tiesioginis ryšys

Vietinis ir tiesioginis ryšys

Kiekviena LAB gali išvesti 60 ALM išėjimų. Jų poaibis gali tiesiogiai valdyti LAB įvestis, tačiau bet kokiam ryšiui su kita eilute ar stulpeliu reikia naudoti bent vieną bendrosios paskirties maršruto laidą.

Vietinis sujungimas valdo ALM įėjimus. ALM išėjimai, taip pat stulpelių ir eilučių jungtys valdo vietinį sujungimą.

3 pav. „Intel Agilex LAB“ vietinis ir tiesioginis ryšys  Carry Chain jungtys

Carry Chain jungtys

Tarp ALM yra specialus perdavimo grandinės kelias. „Intel Agilex“ įrenginiuose yra patobulinta LAB sujungimo struktūra, skirta transportavimo grandinėms nukreipti efektyvioms aritmetinėms funkcijoms atlikti. Šie ALM–ALM ryšiai apeina vietinį sujungimą.

„Intel Hyperflex“ registrai pridedami prie perdavimo grandinės, kad būtų galima lanksčiai nustatyti LAB grandinę, o „Intel Quartus Prime Compiler“ automatiškai pasinaudojatage iš šių išteklių pagerinti panaudojimą ir našumą.

4 pav. Carry Chain jungtys LAB valdymo signalai

LAB valdymo signalai

Kiekviename LAB valdymo bloke yra du laikrodžio šaltiniai, kurie generuoja du LAB laikrodžius (LABCLK[1:0]) ir du uždelstus LAB laikrodžius (LABCLK_Phi1[1:0]), kad valdytų LAB ALM registrus ir hiperregistrus. LAB palaiko du unikalius laikrodžio įjungimo signalus, taip pat papildomus aiškius signalus, skirtus ALM registrams.

LAB eilučių laikrodžiai [5..0] ir LAB vietiniai sujungimai generuoja LAB masto valdymo signalus. Žemo pasvirimo laikrodžio tinklas paskirsto pasaulinius signalus eiliniams laikrodžiams [5..0]. „MultiTrack“ jungtį sudaro nuolatinės, pagal našumą optimizuotos skirtingo ilgio ir greičio maršruto linijos, naudojamos maršruto parinkimo efektyvumui užtikrinti. „Intel Quartus Prime Compiler“ automatiškai nukreipia svarbius projektavimo kelius greitesniais sujungimais, kad pagerintų dizaino našumą ir optimizuotų įrenginio išteklius.

Aiškus loginis valdymas

LAB pločio signalai valdo ALM registro aiškaus signalo logiką. ALM registras tiesiogiai palaiko ir sinchroninį, ir asinchroninį išvalymą. Kiekviena LAB palaiko vieną sinchroninį išvalymo signalą ir du asinchroninius išvalymo signalus.

„Intel Agilex“ įrenginiuose yra viso įrenginio atstatymo kaištis (DEV_CLRn), kuris iš naujo nustato visus įrenginio registrus. Prieš kompiliuodami galite įjungti DEV_CLRn kaištį „Intel Quartus Prime“ programinėje įrangoje. Viso įrenginio atstatymo signalas nepaiso visų kitų valdymo signalų.

5 pav. „Intel Agilex LAB-Wide“ valdymo signalai

ALM

Tolesniuose skyriuose aprašomi ALM ištekliai, ALM išvestis ir ALM darbo režimai.

ALM ištekliai

Kiekviename ALM yra įvairių LUT pagrįstų išteklių, kuriuos galima padalyti į du kombinuotus adaptyvius LUT (ALUT), dviejų bitų pilną sumatorių ir keturis registrus.

Su iki aštuonių dviejų kombinuotų ALUT įėjimų, vienas ALM gali įgyvendinti įvairius dviejų funkcijų derinius. Šis pritaikymas leidžia ALM būti visiškai suderinamam su keturiomis įvesties LUT architektūromis. Vienas ALM taip pat gali įgyvendinti aštuonių įvesties funkcijų poaibį.

Viename ALM yra keturi programuojami registrai. Kiekvienas registras turi šiuos prievadus:

- Duomenys įvesti

- Išvesti duomenys

- Normalus LAB laikrodis

- Uždelstas LAB laikrodis

- Laikrodžio įjungimas

- Sinchroninis skaidrus

- Asinchroninis skaidrus

Visuotiniai signalai, bendrosios paskirties įvesties / išvesties (GPIO) kaiščiai arba bet kokia vidinė logika gali valdyti ALM registro laikrodžio įjungimo signalą, laikrodį ir asinchroninius arba sinchroninius aiškius valdymo signalus. Laikrodžio įjungimo signalas turi pirmenybę prieš sinchroninį atstatymo signalą.

Naudojant kombinuotas funkcijas, registrai apeinami, o paieškos lentelės (LUT) ir sumatorių išvestis nukreipiama tiesiai į ALM išvestis. Galimi du greiti išėjimai 6 LUT išėjimui ir 5 apatiniai LUT išėjimai, kad būtų galima apeiti išvesties mux ir prisijungti prie kitos LAB, kad būtų galima sureguliuoti kritinį kelią.

6 pav. „Intel Agilex ALM“ aukšto lygio blokų schema

ALM išvestis

ALM išvestis

Bendrieji kiekvieno ALM maršruto parinkimo išėjimai valdo vietinius, eilučių ir stulpelių nukreipimo išteklius. Šeši ALM išėjimai, įskaitant du greitus išvesties kelius, gali paskatinti stulpelių, eilučių arba tiesioginio ryšio maršruto parinkimo ryšius.

LUT, sumatoriaus arba registro išvestis gali valdyti ALM išvestis. Tiek LUT, tiek papildiklis, ir ALM registras gali vienu metu išeiti iš ALM.

Registrų paketas pagerina įrenginio naudojimą, nes leidžia nesusijusius registrus ir kombinuotą logiką supakuoti į vieną ALM. ALM taip pat gali pašalinti registruotas ir neregistruotas LUT arba papildiklio išvesties versijas.

Toliau pateiktame paveikslėlyje parodytas „Intel Agilex ALM“ ryšys. „Intel Quartus Prime Resource Property Editor“ visas ALM ryšys yra supaprastintas. Kai kurie maršrutai bus nukreipti viduje, naudojant „Intel Quartus Prime“ programinę įrangą.

7 pav. Išsami informacija apie „Intel Agilex ALM“ ryšį ALM veikimo režimai

ALM veikimo režimai

Intel Agilex ALM veikia bet kuriuo iš šių režimų:

- Normalus režimas

- Išplėstas LUT režimas

- Aritmetinis režimas

Normalus režimas

Įprastas režimas leidžia įdiegti dvi funkcijas viename Intel Agilex ALM arba vieną funkciją iki šešių įėjimų.

Iki aštuonių duomenų įvesčių iš LAB vietinio sujungimo yra kombinacinės logikos įvestys.

ALM gali palaikyti tam tikrus visiškai nepriklausomų funkcijų derinius ir įvairius funkcijų, turinčių bendrus įėjimus, derinius.

„Intel Quartus Prime Compiler“ automatiškai parenka įvestis į LUT. Įprastu režimu ALM palaiko registrų pakavimą.

Toliau pateiktame paveikslėlyje parodytas skirtingų LUT režimo įvesties jungčių derinys. Kompiliavimo metu „Intel Quartus Prime“ programinė įranga gali priskirti skirtingus įvesties pavadinimus.

8 pav. ALM įprastu režimu

Taip pat palaikomi funkcijų deriniai su mažiau įėjimų nei parodyta. Pavyzdžiui,ample, palaikomi funkcijų deriniai su tokiu įėjimų skaičiumi.

- 4 ir 3

- 3 ir 3

- 3 ir 2

- 5 ir 2

Norint supakuoti dvi 5 įėjimų funkcijas į vieną ALM, funkcijos turi turėti bent du bendrus įėjimus. Įprastos įvestys yra dataa ir datab. 4 įvesties funkcijos derinys su 5 įvesties funkcija reikalauja vienos bendros įvesties (dataa arba datab).

Retai naudojamame įrenginyje funkcijas, kurios gali būti įtrauktos į vieną ALM, Intel Quartus Prime programinė įranga gali įdiegti atskiruose ALM, kad būtų pasiektas geriausias galimas našumas. Kai įrenginys pradeda pildytis, „Intel Quartus Prime“ programinė įranga automatiškai išnaudoja visas „Intel Agilex ALM“ galimybes. „Intel Quartus Prime Compiler“ automatiškai ieško funkcijų naudodamas bendrus įvestis arba visiškai nepriklausomas funkcijas, kurios turi būti įtrauktos į vieną ALM, kad būtų galima efektyviai panaudoti įrenginio išteklius. Be to, galite rankiniu būdu valdyti išteklių naudojimą nustatydami vietos priskyrimus.

9 pav. 6 įėjimų LUT režimo funkcija įprastu režimu

10 pav. 3 įėjimų LUT režimo funkcija įprastu režimu

10 pav. 3 įėjimų LUT režimo funkcija įprastu režimu

duomenys ir duomenys b yra prieinami registro pakavimui.  Galite įdiegti bet kurią nuo trijų iki šešių įvesties funkciją naudodami šiuos įvestis:

Galite įdiegti bet kurią nuo trijų iki šešių įvesties funkciją naudodami šiuos įvestis:

- datae

- datad0

- datac0

- datac1

- datad1

- dataf

- dataa ir datab – kai dataa ir datab bendrinami abiejuose LUT, kad būtų galima lanksčiai įgyvendinti skirtingą funkciją kiekvienoje LUT.

Tiek dataa, tiek duomenų įvestis palaiko registro pakavimo funkciją. Jei įjungsite registro pakavimo funkciją, ir dataa, ir datab įvestis arba viena iš įėjimų apeina LUT ir tiesiogiai įvedama į registrą, priklausomai nuo naudojamo supakuoto registro režimo. „Intel Agilex“ įrenginiuose palaikomi šie supakuotų registrų režimų tipai:

- 5 įėjimų LUT su 1 supakuotu registro keliu

- 5 įėjimų LUT su 2 supakuotais registro keliais

- Du 3 įėjimų LUT su 2 supakuotais registro keliais

3 įėjimų LUT su 2 supakuotais registro keliais pavaizduotas 3 įėjimų LUT režimo funkcijos įprastu režimu paveikslėlyje. „Intel Agilex“ įrenginiuose 6 įėjimų LUT režimas nepalaiko registrų pakavimo funkcijos.

Išplėstas LUT režimas

11 pav. Palaikomos 8 įėjimų funkcijos išplėstiniame LUT režime

Tam tikros 8 įėjimų funkcijos gali būti įdiegtos viename ALM naudojant visus LUT įėjimus:

- datae

- datad0

- datac0

- dataa

- duomenųb

- datac1

- datad1

- dataf

8 įėjimų išplėstiniame LUT režime palaikomas supakuoto registro režimas, jei supakuotas registras dalijasi duomenų arba duomenų įvestimi su 8 įėjimų LUT.

Aritmetinis režimas

ALM aritmetiniu režimu naudoja du dviejų 4 įvesties LUT rinkinius ir du tam skirtus pilnus sumatorius. Specialūs papildikliai leidžia LUT atlikti išankstinio papildymo logiką. Todėl kiekvienas sumatorius gali pridėti dviejų 4 įvesties funkcijų išvestį.

Aritmetinis režimas taip pat siūlo laikrodžio įjungimą, skaitiklio įjungimą, sinchroninį valdymą aukštyn ir žemyn, pridėjimo ir atėmimo valdymą bei sinchroninį išvalymą.

Išvalymo ir laikrodžio įjungimo parinktys yra visos LAB signalai, turintys įtakos visiems LAB registrams. Galite atskirai išjungti arba įjungti šiuos signalus kiekvienai adaptyviojo LUT (ALUT) registrų porai. „Intel Quartus Prime“ programinė įranga automatiškai įkelia visus registrus, kurių skaitiklis nenaudoja, į kitas LAB.

12 pav. Intel Agilex ALM aritmetiniu režimu

Nešiojimo grandinė

Nešiojimo grandinė

Pernešimo grandinė užtikrina greitą pernešimo funkciją tarp tam skirtų sumatorių aritmetiniu režimu.

2 bitų nešiojimo pasirinkimo funkcija Intel Agilex įrenginiuose padalija perdavimo grandinių sklidimo delsą su ALM. Nešiojimo grandinės gali prasidėti pirmajame arba šeštajame LAB ALM. Galutinis perdavimo signalas nukreipiamas į ALM, kur jis tiekiamas į vietines, eilučių ar stulpelių jungtis.

„Intel Agilex“ loginių masyvo blokų ir adaptyviųjų logikos modulių vartotojo vadovo dokumento peržiūros istorija

| Dokumento versija | Pakeitimai |

| 2022.05.24 | Atnaujintas paveikslas: „Intel Agilex ALM“ aukšto lygio blokinė diagrama. |

| 2019.11.14 | Atnaujintas aprašymas skiltyje LAB valdymo signalai. |

| 2019.10.01 |

|

| 2019.04.02 | Pradinis išleidimas. |

Intel korporacija.

Visos teisės saugomos. „Intel“, „Intel“ logotipas ir kiti „Intel“ ženklai yra „Intel Corporation“ arba jos dukterinių įmonių prekių ženklai. „Intel“ garantuoja savo FPGA ir puslaidininkinių produktų veikimą pagal dabartines specifikacijas pagal standartinę „Intel“ garantiją, tačiau pasilieka teisę bet kuriuo metu be įspėjimo keisti bet kokius gaminius ir paslaugas. „Intel“ neprisiima jokios atsakomybės ar įsipareigojimų, kylančių dėl bet kokios čia aprašytos informacijos, produkto ar paslaugos taikymo ar naudojimo, išskyrus atvejus, kai „Intel“ aiškiai sutiko raštu. „Intel“ klientams patariama įsigyti naujausią įrenginio specifikacijų versiją prieš pasikliaujant bet kokia paskelbta informacija ir prieš užsakant produktus ar paslaugas.

*Kiti pavadinimai ir prekės ženklai gali būti laikomi kitų nuosavybe.

ISO

9001:2015

Registruotas

Dokumentai / Ištekliai

|

intel Agilex loginio masyvo blokai ir adaptyvieji logikos moduliai [pdfVartotojo vadovas „Agilex“ logikos masyvo blokai ir adaptyvieji loginiai moduliai, „Agilex“, loginiai masyvo blokai ir adaptyvieji loginiai moduliai, masyvo blokai ir adaptyvieji logikos moduliai, adaptyvieji logikos moduliai, loginiai moduliai |