intel AN 805 hierarchinė dalinė dizaino perkonfigūracija Arria 10 SoC plėtros plokštėje

Hierarchinė dalinio perkonfigūravimo pamoka, skirta „Intel® Arria® 10 SoC“ kūrimo plokštėms

Šioje programos pastaboje demonstruojamas paprasto dizaino pavertimas hierarchiškai iš dalies perkonfigūruojamu dizainu ir dizaino įgyvendinimas Intel® Arria® 10 SoC kūrimo plokštėje. Hierarchinis dalinis perkonfigūravimas (HPR) yra specialus dalinio perkonfigūravimo (PR) tipas, kai PR regionas yra kitame PR regione. Galite sukurti kelias asmenybes tiek antriniams, tiek pirminiams skaidiniams. Antrinius skaidinius įdedate į pirminius skaidinius. Antrinio skaidinio perkonfigūravimas neturi įtakos darbui pirminiuose ar statiniuose regionuose. Pirminio skaidinio perkonfigūravimas neturi įtakos operacijai statiniame regione, bet pakeičia pirminio regiono antrinius skaidinius numatytosiomis antrinio skaidinio asmenybėmis. Ši metodika yra efektyvi sistemose, kuriose kelios funkcijos naudojasi tuo pačiu FPGA įrenginio ištekliu.

Dalinis perkonfigūravimas suteikia šiuos plokščio dizaino patobulinimus:

- Leidžia iš naujo konfigūruoti vykdymo laiką

- Padidina dizaino mastelio keitimą

- Sumažina sistemos prastovos laiką

- Palaiko dinamines laiko multipleksavimo funkcijas projektuojant

- Sumažina sąnaudas ir energijos sąnaudas efektyviai išnaudojant lentos erdvę

- Pastaba:

- Norint įgyvendinti šį etaloninį dizainą, reikia išmanyti „Intel Quartus® Prime FPGA“ diegimo srautą ir žinoti pirminį „Intel Quartus Prime“ projektą. files.

Susijusi informacija

- „Intel Arria 10 SoC Development Kit“ vartotojo vadovas

- Dalinio perkonfigūravimo koncepcijos

- Dalinės konfigūracijos projektavimo srautas

- Dalinės konfigūracijos projektavimo rekomendacijos

- Dalinės konfigūracijos projektavimo svarstymai

Nuorodų projektavimo reikalavimai

Šiam etaloniniam dizainui reikia:

- „Intel Quartus Prime Pro Edition“ programinės įrangos versija 17.1, skirta dizaino įgyvendinimui.

- Intel Arria 10 SoC kūrimo rinkinys, skirtas FPGA diegimui.

Intel korporacija. Visos teisės saugomos. „Intel“, „Intel“ logotipas ir kiti „Intel“ ženklai yra „Intel Corporation“ arba jos dukterinių įmonių prekių ženklai. „Intel“ garantuoja savo FPGA ir puslaidininkinių produktų veikimą pagal dabartines specifikacijas pagal standartinę „Intel“ garantiją, tačiau pasilieka teisę bet kuriuo metu be įspėjimo keisti bet kokius gaminius ir paslaugas. „Intel“ neprisiima jokios atsakomybės ar įsipareigojimų, kylančių dėl bet kokios čia aprašytos informacijos, produkto ar paslaugos taikymo ar naudojimo, išskyrus atvejus, kai „Intel“ aiškiai sutiko raštu. „Intel“ klientams patariama įsigyti naujausią įrenginio specifikacijų versiją prieš pasikliaujant bet kokia paskelbta informacija ir prieš užsakant produktus ar paslaugas.

- Kiti pavadinimai ir prekės ženklai gali būti laikomi kitų nuosavybe.

Nuorodų dizainas baigtasview

- Šis pamatinis dizainas susideda iš vieno 32 bitų skaitiklio. Plokštės lygiu dizainas prijungia laikrodį prie 50 MHz šaltinio ir jungia išvestį prie keturių FPGA šviesos diodų. Pasirinkus išvestį iš skaitiklių bitų tam tikra seka, šviesos diodai mirksi tam tikru dažniu.

1 pav. Plokščias etaloninis dizainas be PR skaidymo

Nuorodų dizainas Files

Dalinio perkonfigūravimo mokymo programą galima rasti šioje vietoje: https://github.com/intel/fpga-partial-reconfig

Norėdami atsisiųsti mokymo programą:

- Spustelėkite Klonuoti arba atsisiųsti.

- Spustelėkite Atsisiųsti ZIP. Išpakuokite FPGA-partial-config-master.zip file.

- Eikite į tutorials/a10_soc_devkit_blinking_led_hpr poaplankį, kad pasiektumėte nuorodos dizainą.

Plokščiasis aplankas susideda iš šių elementų files:

1 lentelė. Standartinis dizainas Files

| File Vardas | Aprašymas |

| viršuje. SV | Aukščiausio lygio file yra plokščias dizaino įgyvendinimas. Šis modulis sukuria blinking_led antrinį skaidinį ir top_counter modulį. |

| top_counter.sv | Aukščiausio lygio 32 bitų skaitiklis, tiesiogiai valdantis LED[1]. Registruota skaitiklio išvestis valdo LED[0], taip pat maitina LED[2] ir LED[3] per blinking_led modulį. |

| blinking_led.sdc | Apibrėžia projekto laiko apribojimus. |

| tęsėsi… | |

| File Vardas | Aprašymas |

| blinking_led.SV | Šiame vadove šį modulį konvertuosite į pagrindinį PR skaidinį. Modulis gauna registruotą top_counter modulio išvestį, kuris valdo LED[2] ir LED[3]. |

| blinking_led.qpf | „Intel Quartus Prime“ projektas file kuriame yra visų projekto pataisymų sąrašas. |

| blinking_led.qsf | Intel Quartus Prime nustatymai file kuriame yra projekto užduotys ir nustatymai. |

Pastaba: Aplanke hpr yra visas rinkinys files kuriate naudodami šią programos pastabą. Pateikite nuorodą į šiuos files bet kuriuo perėjimo momentu.

2 pav. Etaloninis dizainas Files

Nuorodų dizaino apžvalga

Tolesniuose žingsniuose aprašomas dalinio perkonfigūravimo taikymas plokščiam dizainui. Mokomojoje programoje naudojama Intel Quartus Prime Pro Edition programinė įranga, skirta Intel Arria 10 SoC kūrimo plokštei:

- 1 veiksmas: Darbo pradžia 6 puslapyje

- 2 veiksmas: Sukurkite vaiko lygio submodulį 6 puslapyje

- 3 veiksmas: Dizaino pertvarų kūrimas 7 puslapyje

- 4 veiksmas: PR skaidinių vietos ir maršruto parinkimo regiono paskirstymas 9 puslapyje

- 5 veiksmas: „Intel Arria 10“ dalinio perkonfigūravimo valdiklio IP branduolio pridėjimas 10 puslapyje

- 6 veiksmas: Asmenų apibrėžimas 13 puslapyje

- 7 veiksmas: Pataisų kūrimas 15 puslapyje

- 8 veiksmas: Hierarchinio dalinio perkonfigūravimo srauto scenarijaus generavimas 20 puslapyje

- 9 veiksmas: Hierarchinio dalinio perkonfigūravimo srauto scenarijaus vykdymas 21 puslapyje

- 10 veiksmas: Plokštės programavimas 22 puslapyje

1 veiksmas: darbo pradžia

Norėdami nukopijuoti pamatinį dizainą files į savo darbo aplinką ir sukurkite blinking_led plokščią dizainą:

- Sukurkite katalogą savo darbo aplinkoje a10_soc_devkit_blinking_led_hpr.

- Nukopijuokite atsisiųstus vadovėlius/a10_soc_devkit_blinking_led_hpr/flat poaplankį į katalogą a10_soc_devkit_blinking_led_hpr.

- „Intel Quartus Prime Pro Edition“ programinėje įrangoje spustelėkite File ➤ Atidarykite projektą ir pasirinkite blinking_led.qpf.

- Norėdami sudaryti plokščią dizainą, spustelėkite Apdorojimas ➤ Pradėti kompiliavimą.

2 veiksmas: vaiko lygio submodulio kūrimas

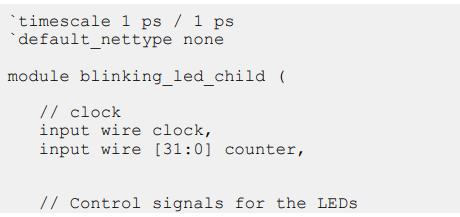

Norėdami konvertuoti šį plokščią dizainą į hierarchinį PR dizainą, turite sukurti antrinį submodulį (blinking_led_child. SV), kuris yra įdėtas pirminiame submodulyje (blinking_led.sv).

- Sukurkite naują dizainą file, blinking_led_child.sv ir prie jo pridėkite šias kodo eilutes file: laiko skalė 1 ps / 1 ps `default_nettype none module blinking_led_child ( // laikrodžio įvesties laido laikrodis, įvesties laido [31:0] skaitiklis, // Šviesos diodų valdymo signalai

- Pakeiskite blinking_led.sv file prijungti led_two_on prie skaitiklio 23 bito iš statinės srities ir sukurti blinking_led_child modulį. Po pakeitimų jūsų blinking_led.sv file turi pasirodyti taip:

- Keičiant visą dizainą files, iš naujo sukompiliuokite projektą spustelėdami Apdorojimas ➤ Pradėti kompiliavimą

3 veiksmas: dizaino pertvarų kūrimas

Turite sukurti projektavimo skaidinius kiekvienam PR regionui, kurį norite iš dalies konfigūruoti. Savo dizaine galite sukurti bet kokį nepriklausomų skaidinių ar PR regionų skaičių. Šioje mokymo programoje sukuriami du projektavimo skaidiniai, skirti u_blinking_led_child ir u_blinking_led egzemplioriams.

Norėdami sukurti dizaino skaidinius hierarchiniam daliniam perkonfigūravimui:

- Dešiniuoju pelės mygtuku spustelėkite u_blinking_led_child egzempliorių projektų naršymo priemonėje ir spustelėkite Projektavimo skaidinys ➤ Nustatyti kaip projektavimo skaidinį. Projektavimo skaidinio piktograma rodoma šalia kiekvieno egzemplioriaus, kuris nustatytas kaip skaidinys.

3 pav. Dizaino pertvarų kūrimas naudojant Project Navigator

- Norėdami apibrėžti skaidinio tipą, dešiniuoju pelės mygtuku spustelėkite u_blinking_led_child egzempliorių skirtuke Hierarchija, spustelėkite Dizaino skaidinys ➤ Perkonfigūruojamas. Galite apibrėžti skaidinio tipą tik nustatę egzempliorių kaip skaidinį. Projektavimo skaidinys rodomas užduotyse View Skirtuko projektavimo pertvaros langas.

4 pav. Dizaino pertvarų langas

- Redaguokite skaidinio pavadinimą projektavimo pertvarų lange dukart spustelėdami pavadinimą. Šiam pamatiniam dizainui pervardykite skaidinio pavadinimą į pr_partition.

Pastaba: Kai kuriate skaidinį, „Intel Quartus Prime“ programinė įranga automatiškai sugeneruoja skaidinio pavadinimą pagal egzemplioriaus pavadinimą ir hierarchijos kelią. Šis numatytasis skaidinio pavadinimas gali skirtis kiekvienu atveju. - Pakartokite 1 ir 2 veiksmus, kad priskirtumėte perkonfigūruojamus dizaino skaidinius u_blinking_led egzemplioriui. Pervardykite šį skaidinį į pr_parent_partition.

Patikrinkite, ar blinking_led.qsf yra šios priskyrimai, atitinkantys jūsų perkonfigūruojamus dizaino skaidinius:

Sukurkite projektines pertvaras daliniam perkonfigūravimui

4 veiksmas: Viešųjų ryšių skaidinių vietos ir maršruto parinkimo regiono paskirstymas

Kai kuriate bazinę versiją, PR projektavimo srautas naudoja jūsų PR skaidinio regiono paskirstymą, kad atitinkamas asmens branduolys būtų įtrauktas į rezervuotą regioną. Norėdami rasti ir priskirti PR regioną įrenginio aukšto plane pagal pagrindinę versiją:

- Dešiniuoju pelės mygtuku spustelėkite u_blinking_led_child egzempliorių projektų naršymo priemonėje ir spustelėkite Logic Lock region ➤ Sukurti naują loginio užrakto regioną. Regionas rodomas Logic Lock Regions lange.

- Jūsų paskirties vietos regione turi būti blinking_led_child logika. Pasirinkite paskirties vietą, surasdami mazgą lustų planavimo priemonėje. Dešiniuoju pelės mygtuku spustelėkite u_blinking_led_child regiono pavadinimą projektų naršymo priemonėje ir spustelėkite Rasti mazgą ➤ Rasti lustų planavimo priemonėje.

5 pav. Lustų planavimo mazgo vieta, skirta blinking_led

- Lango Logic Lock Regions stulpelyje Origin nurodykite paskirties vietos koordinates. Kilmė atitinka apatinį kairįjį regiono kampą. Pavyzdžiui,ample, norėdami nustatyti paskirties vietą su (X1 Y1) koordinatėmis kaip (69 10), nurodykite kilmę kaip X69_Y10. „Intel Quartus Prime“ programinė įranga automatiškai apskaičiuoja (X2 Y2) koordinates (viršuje dešinėje) paskirties regionui, atsižvelgdama į jūsų nurodytą aukštį ir plotį.

Pastaba: Šioje mokymo programoje naudojamos (X1 Y1) koordinatės – (69 10), o aukštis ir plotis – 20 paskirties vietai. Apibrėžkite bet kokią paskirties vietos regiono reikšmę, jei ši sritis apima blinking_led_child logiką. - Įgalinkite rezervuotas ir tik pagrindines parinktis.

- Dukart spustelėkite parinktį Routing Region. Pasirodo dialogo langas Logic Lock Routing Region Settings.

- Maršruto parinkimo tipui pasirinkite Fiksuota su išplėtimu. Pasirinkus šią parinktį, automatiškai priskiriamas 1 išplėtimo ilgis.

Pastaba: Maršruto parinkimo sritis turi būti didesnė už įdėjimo sritį, kad montuotojui būtų suteikta daugiau lankstumo, kai variklis nukreipia skirtingus asmenis. - Pakartokite 1–6 veiksmus u_blinking_led egzemplioriui. Pirminio lygio paskirties vieta Pakartokite 1–6 veiksmus u_blinking_led egzemplioriui. Pirminio lygio paskirties vietos regionas turi visiškai apimti atitinkamas antrinio lygio paskirties vietos ir maršruto parinkimo sritis, paliekant pakankamai vietos pirminio lygio loginei vietai. Šioje mokymo programoje naudojamos (X1 Y1) koordinatės – (66 7), aukštis 47 ir plotis 26 u_blinking_led egzemplioriaus išdėstymo sričiai.

6 pav. Loginio užrakto regionų langas

Patikrinkite, ar blinking_led.qsf yra šios užduotys, atitinkančios jūsų grindų planavimą:

- Aukšto plano dalinės pertvarkymo projektas

- Laipsniškas dalinio perkonfigūravimo įgyvendinimas

5 veiksmas: pridėkite „Intel Arria 10“ dalinio perkonfigūravimo valdiklio IP branduolį

- Norėdami iš naujo sukonfigūruoti PR skaidinį, naudokite „Intel Arria 10 Partial Reconfiguration Controller“ IP branduolį. Šis IP branduolys naudoja JTAG norėdami iš naujo sukonfigūruoti PR skaidinį. Norėdami pridėti „Intel Arria 10 Partial Reconfiguration Controller“ IP branduolį prie savo „Intel Quartus Prime“ projekto:

- IP kataloge įveskite Dalinis perkonfigūravimas.

- Norėdami paleisti IP Parameter Editor Pro langą, iš IP bibliotekos pasirinkite Intel Arria 10 Partial Reconfiguration Controller IP branduolį ir spustelėkite Pridėti.

- Dialogo lange Naujas IP variantas įveskite pr_ip kaip file pavadinimą ir spustelėkite Sukurti. Naudokite numatytąjį pr_ip parametrizavimą. Įsitikinkite, kad Įjungti JTAG Derinimo režimas ir Įjungti sąsajos užšaldymą parinktys įjungtos, o parinktis Įgalinti „Avalon-MM slave“ sąsają – išjungta.

7 pav. Intel Arria 10 dalinio perkonfigūravimo valdiklio IP pagrindiniai parametrai

- Spustelėkite Baigti ir išeikite iš parametrų rengyklės nesugeneruodami sistemos. „Intel Quartus Prime“ programinė įranga sukuria pr_ip.ip IP variantą fileir prideda file į blinking_led projektą.

Pastaba:

- Jei kopijuojate pr_ip.ip file iš aplanko hpr rankiniu būdu redaguokite blinking_led.qsf file įtraukti šią eilutę: set_global_assignment -name IP_FILE pr_ip.ip

- Įdėkite IP_FILE priskyrimas po SDC_FILE užduotys (jtag.sdc ir blinking_led.sdc) jūsų blinking_led.qsf file. Šis užsakymas užtikrina tinkamą dalinio perkonfigūravimo IP branduolio apribojimą.

Pastaba: Norėdami aptikti laikrodžius, SDC file PR IP turi atitikti bet kurį SDC, kuris sukuria IP branduolio naudojamus laikrodžius. Supaprastinate šį užsakymą užtikrindami .ip file PR IP branduolys yra po bet kurio .ip files arba SDC files naudojami šiems laikrodžiams sukurti QSF file jūsų „Intel Quartus Prime“ projekto peržiūrai. Norėdami gauti daugiau informacijos, žr. dalinio perkonfigūravimo IP pagrindinio vartotojo vadovo skyrių Laiko apribojimai.

Susijusi informacija

- Dalinio perkonfigūravimo IP sprendimų vartotojo vadovas

- Norėdami gauti informacijos apie dalinio perkonfigūravimo regiono valdiklio IP branduolį.

- Dalinio perkonfigūravimo IP pagrindinio vartotojo vadovas

- Norėdami gauti informacijos apie laiko apribojimus.

Aukščiausio lygio dizaino atnaujinimas

Norėdami atnaujinti top.SV file su PR_IP pavyzdžiu:

- Norėdami pridėti PR_IP egzempliorių prie aukščiausio lygio dizaino, panaikinkite toliau pateikto kodo bloko viršuje esantį komentarą.SV file:

- Norėdami priversti išvesties prievadus į logiką 1 perkonfigūravimo metu, naudokite fiksavimo valdymo signalo išvestį iš PR_IP. Tačiau norint stebėti, kaip šviesos diodas toliau mirksi iš pirminės PR skaidinio, kai PR programuoja antrinę sritį, užšalimo valdymo signalas neišjungia led_two_on. Įsitikinkite, kad pr_led_two_on yra tiesiogiai

- Norėdami priskirti numatytosios pirminės asmenybės egzempliorių (blinking_led), atnaujinkite top.SV file su šiuo kodo bloku:

8 pav. Dalinis perkonfigūravimas IP pagrindinio integravimo

6 veiksmas: asmenybių apibrėžimas

Šis orientacinis dizainas apibrėžia penkias atskiras asmenybes pagrindinio ir antrinio PR skaidiniams. Norėdami apibrėžti ir įtraukti asmenis į savo projektą:

- Sukurkite keturis SystemVerilog files, blinking_led_child.sv, blinking_led_child_slow.sv, blinking_led_child_empty.sv ir blinking_led_slow.sv penkių asmenų darbo kataloge.

Pastaba: Jei sukuriate SystemVerilog files iš Intel Quartus Prime teksto rengyklės, išjunkite Add file į esamą projekto parinktį, išsaugant files.

2 lentelė. Referencinių dizaino personų

| File Vardas | Aprašymas | Kodas |

| blinking_led_child.sv | Vaiko lygio dizaino numatytoji asmenybė |

`laikas 1 ps / 1 ps `default_nettype none module blinking_led_child ( // laikrodis įvesties laidinis laikrodis, įvesties laido [31:0] skaitiklis,

// Valdymo signalai šviesos diodų išvesties laidui led_three_on

); vietinis parametras COUNTER_TAP = 23; reg led_trys_on_r;

priskirti led_trys_įjungta = led_trys_on_r; Always_ff @(posedge clock) prasideda led_trys_on_r <= skaitiklis[COUNTER_TAP]; galas

pabaigos modulis |

| tęsėsi… | ||

| File Vardas | Aprašymas | Kodas |

| blinking_led_child_slow.sv | The

LED_THREE mirksi lėčiau |

`laikas 1 ps / 1 ps `default_nettype nėra

modulis blinking_led_child_slow (

// laikrodis įvesties laidinis laikrodis, įvesties laido [31:0] skaitiklis,

// Valdymo signalai šviesos diodų išvesties laidui led_three_on );

vietinis parametras COUNTER_TAP = 27; reg led_trys_on_r;

priskirti led_trys_įjungta = led_trys_on_r; Always_ff @(posedge clock) prasideda led_trys_on_r <= skaitiklis[COUNTER_TAP]; pabaiga

pabaigos modulis |

| blinking_led_child_empty.sv | The

LED_THREE lieka ĮJUNGTA |

`laikas 1 ps / 1 ps `default_nettype nėra

modulis blinking_led_child_empty (

// laikrodis įvesties laidinis laikrodis, įvesties laido [31:0] skaitiklis,

// Valdymo signalai šviesos diodų išvesties laidui led_three_on

);

// Šviesos diodas veikia žemai priskirti led_three_on = 1'b0;

pabaigos modulis |

| blinking_led_slow.sv | LED_TWO

mirksi lėčiau. |

`laikas 1 ps / 1 ps `default_nettype none module blinking_led_slow( // laikrodis įvesties laidinis laikrodis, įvesties laido [31:0] skaitiklis,

// LED išvesties laido valdymo signalai led_two_on, išvesties laidas LED_trys_įjungtas

);

vietinis parametras COUNTER_TAP = 27; reg led_two_on_r; priskirti led_two_on = led_two_on_r;

// Prekystalis: always_ff @(posedge clock) begin led_dwo_on_r <= counter[COUNTER_TAP]; pabaiga

blinking_led_child u_blinking_led_child( .led_three_on (led_three_on), .skaitiklis (skaitiklis), .clock (laikrodis) |

| File Vardas | Aprašymas | Kodas |

| );ndmodule |

3 veiksmas: dizaino pertvarų kūrimas 7 puslapyje

7 veiksmas: pataisymų kūrimas

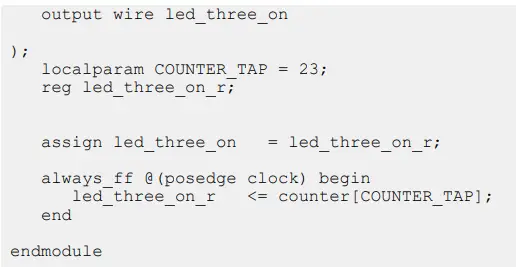

PR projektavimo srautas naudoja „Intel Quartus Prime“ programinės įrangos projekto peržiūrų funkciją. Jūsų pradinis dizainas yra pagrindinė versija, kurioje apibrėžiate statines regiono ribas ir perkonfigūruojamas sritis FPGA. Iš pagrindinės versijos sukuriate kelias versijas. Šiose pataisose pateikiami skirtingi PR regionų diegimai. Tačiau visose PR diegimo versijose naudojami tie patys aukščiausio lygio išdėstymo ir maršruto parinkimo rezultatai iš pagrindinės versijos. Norėdami sudaryti PR dizainą, turite sukurti kiekvieno asmens PR įgyvendinimo peržiūrą ir sintezės peržiūrą. Šiame pamatiniame projekte, be pagrindinės versijos (blinking_led), trys vaikų lygio asmenys ir dvi tėvų lygio asmenybės turi penkias atskiras sintezės versijas ir penkias atskiras diegimo versijas:

3 lentelė. Dviejų tėvų ir trijų vaikų asmenybių peržiūros

| Sintezės peržiūra | Įgyvendinimo peržiūra |

| blinking_led_parent, blinking_led_default | blinking_led_pr_alpha |

| blinking_led_parent, blinking_led_child_slow | blinking_led_pr_bravo |

| blinking_led_parent, blinking_led_child_tuščias | blinking_led_pr_charlie |

| blinking_led_parent_slow, blinking_led_child_slow | blinking_led_pr_delta |

| blinking_led_parent_slow, blinking_led_child_empty | blinking_led_pr_emma |

Diegimo peržiūrų kūrimas

Norėdami sukurti PR įgyvendinimo peržiūras:

- Norėdami atidaryti dialogo langą Taisymai, spustelėkite Projektas ➤ Taisymai.

- Norėdami sukurti naują versiją, dukart spustelėkite < >.

- Nurodykite taisymo pavadinimą kaip blinking_led_pr_alpha ir pasirinkite blinking_led laukelyje Based on Revision.

- Išjunkite parinktį Nustatyti kaip dabartinę versiją ir spustelėkite Gerai.

- Panašiai sukurkite blinking_led_pr_bravo, blinking_led_pr_charlie, blinking_led_pr_delta ir blinking_led_pr_emma versijas, atsižvelgdami į blinking_led versiją.

Pastaba: Nenustatykite aukščiau pateiktų pataisų kaip dabartinės versijos.

9 pav. Pataisų kūrimas

Tik sintezei skirtų pataisų kūrimas

Norėdami sukurti tik sintezės asmenybių versijas, turite priskirti aukščiausio lygio objektą ir atitinkamą SystemVerilog file kiekvienai asmenybei:

- „Intel Quartus Prime“ programinėje įrangoje spustelėkite Projektas ➤ Revizijos.

- Sukurkite blinking_led_default versiją pagal blinking_led versiją. Nenustatykite šios pataisos kaip dabartinės versijos.

- Pakeiskite blinking_led_default.qsf file įtraukti šias užduotis:

set_global_assignment -name TOP_LEVEL_ENTITY blinking_led_child

set_global_assignment -name SYSTEMVERILOG_FILE - Panašiai sukurkite blinking_led_child_slow, blinking_led_child_empty, blinking_led_parent ir blinking_led_parent_slow versijas pagal blinking_led peržiūrą. Nenustatykite šių pataisų kaip dabartinių pataisų.

- Atnaujinkite blinking_led_child_slow.qsf, blinking_led_child_empty.qsf, blinking_led_parent.qsf ir blinking_led_parent_slow.qsf files su jų atitinkančiais

TOP_LEVEL_ENTITY ir SYSTEMVERILOG_FILE užduotys:

- Kad išvengtumėte sintezės klaidų, įsitikinkite, kad sintezė bus peržiūrėta files antrinėms pertvaroms nėra jokio projektinio skaidinio, kaiščių priskyrimų ar loginio užrakto

regioninės užduotys. Taip pat sintezės peržiūra filePagrindinių skaidinių s turi būti tik atitinkamų antrinių skaidinių projektinių skaidinių priskyrimai. Pašalinkite šias užduotis, jei tokių yra, iš blinking_led_default.qsf, blinking_led_child_slow.qsf, blinking_led_child_empty.qsf, blinking_led_parent.qsf ir blinking_led_parent_slow.pdf files

- Į blinking_led_parent.qsf ir blinking_led_parent_slow.qsf įtraukite šias užduotis files:

- Patikrinkite, ar blinking_led.qpf file yra šios pataisos, be jokios konkrečios tvarkos:

- Pastaba: Jei kopijuojate pataisą files iš aplanko hpr, rankiniu būdu atnaujinkite blinking_led.qpf file su aukščiau pateiktomis kodo eilutėmis.

Nurodykite peržiūros tipą

Kiekvienai versijai turite priskirti taisymo tipą. Yra trys peržiūrų tipai:

- Dalinis perkonfigūravimas – bazė

- Dalinis perkonfigūravimas – asmenybių sintezė

- Dalinis perkonfigūravimas – asmenybių diegimas

- Šioje lentelėje pateikiami kiekvienos versijos taisymo tipo priskyrimai:

4 lentelė. Revizijų tipai

| Revizijos pavadinimas | Revizijos tipas |

| blinking_led.qsf | Dalinis perkonfigūravimas – bazė |

| blinking_led_default.qsf | Dalinis perkonfigūravimas – asmenybių sintezė |

| blinking_led_child_empty.qsf | Dalinis perkonfigūravimas – asmenybių sintezė |

| blinking_led_child_slow.qsf | Dalinis perkonfigūravimas – asmenybių sintezė |

| blinking_led_parent.qsf | Dalinis perkonfigūravimas – asmenybių sintezė |

| blinking_led_parent_slow.qsf | Dalinis perkonfigūravimas – asmenybių sintezė |

| blinking_led_pr_alpha.qsf | Dalinis perkonfigūravimas – asmenybių diegimas |

| blinking_led_pr_bravo.qsf | Dalinis perkonfigūravimas – asmenybių diegimas |

| blinking_led_pr_charlie.qsf | Dalinis perkonfigūravimas – asmenybių diegimas |

| blinking_led_pr_delta.qsf | Dalinis perkonfigūravimas – asmenybių diegimas |

| blinking_led_pr_emma.qsf | Dalinis perkonfigūravimas – asmenybių diegimas |

- Spustelėkite Projektas ➤ Pataisymai. Pasirodo dialogo langas Revisions.

- Stulpelyje Revision Name pasirinkite blinking_led ir spustelėkite Nustatyti dabartinį.

- Spustelėkite Taikyti. Atsidaro blinking_led versija.

- Norėdami nustatyti blinking_led peržiūros tipą, spustelėkite Užduotys ➤ Nustatymai ➤ Bendra.

- Pasirinkite peržiūros tipą kaip dalinį perkonfigūravimą – bazę.

- Panašiai nustatykite kitų dešimties pataisymų tipus, kaip nurodyta aukščiau esančioje lentelėje.

- Pastaba: Prieš priskirdami taisymo tipą, kiekvieną versiją turite nustatyti kaip dabartinę versiją. Patikrinkite, ar kiekvienas .qsf file yra tokia užduotis:

- Pastaba: Pridėkite visus „Fitter“ specifinius parametrus, kuriuos norite naudoti PR diegimo kompiliacijoje, prie „personal“ diegimo peržiūrų. Konkrečios montuotojo nustatymai turi įtakos asmens tinkamumui, bet neturi įtakos importuojamai statinei sričiai. Taip pat galite pridėti bet kokius su sinteze susijusius nustatymus prie atskirų asmenybių sintezės versijų.

Kurkite „Personų“ pataisas

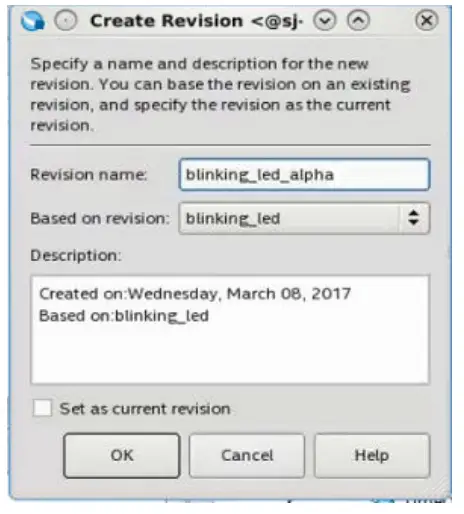

8 veiksmas: Hierarchinio dalinio perkonfigūravimo srauto scenarijaus generavimas

Norėdami sugeneruoti hierarchinį dalinio perkonfigūravimo eigos scenarijų:

- Iš Intel Quartus Prime komandos apvalkalo sukurkite srauto šabloną vykdydami šią komandą:

- „Intel Quartus Prime“ generuoja a10_hier_partial_reconfig/flow.tcl file.

- Pervardykite sugeneruotą a10_hier_partial_reconfig/setup.tcl.example į a10_hier_partial_reconfig/setup.tcl ir modifikuokite scenarijų, kad nurodytumėte dalinio perkonfigūravimo projekto detales:

a. Norėdami apibrėžti projekto pavadinimą, atnaujinkite šią eilutę: b. Norėdami apibrėžti bazinę versiją, atnaujinkite šią eilutę:

b. Norėdami apibrėžti bazinę versiją, atnaujinkite šią eilutę:

- Norėdami apibrėžti kiekvieną dalinio perkonfigūravimo įgyvendinimo versiją, kartu su PR skaidinių pavadinimais ir šaltinio versija, kuri įgyvendina versijas, atnaujinkite šias eilutes:

Pastaba: Visi taisymo projektai turi būti tame pačiame kataloge kaip blinking_led.qpf. Kitu atveju atitinkamai atnaujinkite srauto scenarijų.

9 veiksmas: Hierarchinio dalinio perkonfigūravimo srauto scenarijaus vykdymas

Norėdami paleisti hierarchinį dalinio perkonfigūravimo eigos scenarijų:

- Spustelėkite Įrankiai ➤ Tcl scenarijai. Pasirodo dialogo langas Tcl Scripts.

- Spustelėkite Pridėti prie projekto, naršykite ir pasirinkite a10_hier_partial_reconfig/flow.tcl.

- Bibliotekų srityje pasirinkite a10_hier_partial_reconfig/flow.tcl ir spustelėkite Vykdyti.

Šis scenarijus vykdo trijų asmenybių sintezę. „Intel Quartus Prime“ generuoja SRAM objektą File (.sof), iš dalies užmaskuotas SRAM objektas File (.pmsf) ir neapdorotą dvejetainį failą File (.rbf) kiekvienai asmenybei.

Pastaba: Norėdami paleisti scenarijų iš Intel Quartus Prime komandos apvalkalo, įveskite šią komandą:

- Sudarykite dalinės konfigūracijos projektą

- Dalinio perkonfigūravimo srauto scenarijaus naudojimas

- Dalinio perkonfigūravimo srauto scenarijaus konfigūravimas

- Sukurti programavimą Files

10 veiksmas: Plokštės programavimas

Prieš pradėdami:

- Prijunkite maitinimo šaltinį prie Intel Arria 10 SoC kūrimo plokštės.

- Prijunkite USB Blaster kabelį tarp kompiuterio USB prievado ir kūrimo plokštės USB Blaster prievado.

Norėdami paleisti dizainą Intel Arria 10 SoC kūrimo plokštėje:

- Atidarykite „Intel Quartus Prime“ programinę įrangą ir spustelėkite Įrankiai ➤ Programuotojas.

- Programuotoje spustelėkite Hardware Setup ir pasirinkite USB-Blaster.

- Spustelėkite Auto Detect ir pasirinkite įrenginį, 10AS066N3.

- Spustelėkite Gerai. „Intel Quartus Prime“ programinė įranga aptinka ir atnaujina programuotoją su trimis plokštėje esančiais FPGA lustais.

- Pasirinkite 10AS066N3 įrenginį, spustelėkite Keisti File ir įkelkite blinking_led_pr_alpha.sof file.

- Įgalinti blinking_led_pr_alpha.sof programavimą/konfigūravimą file.

- Spustelėkite Pradėti ir palaukite, kol eigos juosta pasieks 100%.

- Stebėkite, kaip plokštės šviesos diodai mirksi tokiu pat dažniu kaip ir originalus plokščias dizainas.

- Norėdami užprogramuoti tik antrinį PR regioną, dešiniuoju pelės mygtuku spustelėkite blinking_led_pr_alpha.sof file Programuotoje ir spustelėkite Pridėti PR programavimą File.

- Pasirinkite blinking_led_pr_bravo.pr_parent_partition.pr_partition.rbf file.

- Išjungti „blinking_led_pr_alpha.sof“ programą / konfigūravimą file.

- Įgalinti blinking_led_pr_bravo.pr_parent_partition.pr_partition.rbf programą / konfigūravimą file ir spustelėkite Pradėti. Stebėkite, kaip toliau mirksi šviesos diodas [0] ir LED [1]. Kai eigos juosta pasiekia 100%, LED[2] mirksi tokiu pat greičiu, o LED[3] mirksi lėčiau.

- Norėdami užprogramuoti ir pirminį, ir antrinį PR regioną, dešiniuoju pelės mygtuku spustelėkite .rbf file Programuotoje ir spustelėkite Keisti PR programavimą File.

- Pasirinkite blinking_led_pr_delta.pr_parent_partition.rbf file.

- Spustelėkite Pradėti. Stebėkite lentoje, kad LED[0] ir LED[1] toliau mirksi. Kai eigos juosta pasiekia 100%, ir LED[2], ir LED[3] mirksi lėčiau.

- Pakartokite pirmiau nurodytus veiksmus, kad dinamiškai perprogramuotumėte tik antrinį PR regioną arba abu pirminio ir vaiko PR regionus vienu metu.

10 pav. Intel Arria 10 SoC plėtros plokštės programavimas

Esamos asmenybės keitimas

- Galite pakeisti esamą asmenybę net ir visiškai sukūrę bazinę versiją.

- Pavyzdžiui,ample, kad blinking_led_child_slow persona mirksėtų dar lėčiau:

- Blinking_led_child_slow.sv file, pakeiskite parametrą COUNTER_TAP nuo 27 iki 28.

- Norėdami iš naujo susintetinti ir iš naujo įdiegti šią asmenybę, turite iš naujo sukompiliuoti visas tik sintezei skirtas ir įgyvendinimo versijas, kurias paveikė pakeitimas. Modifikuokite setup.tcl scenarijų, kad įtrauktumėte šias eilutes:

Pastaba: Apibrėždami blinking_led_pr_delta versijos pr_parent_parition, importuojate galutinę to asmens momentinę kopiją, kad ji būtų įdiegta. Dėl to pirminio skaidinio logikos įgyvendinimas išlieka toks pat, modifikuojant ir įgyvendinant atitinkamą antrinį skaidinį.

Pastaba: Apibrėždami blinking_led_pr_delta versijos pr_parent_parition, importuojate galutinę to asmens momentinę kopiją, kad ji būtų įdiegta. Dėl to pirminio skaidinio logikos įgyvendinimas išlieka toks pat, modifikuojant ir įgyvendinant atitinkamą antrinį skaidinį. Ši komanda iš naujo sintezuoja blinking_led_child_slow sintezės versiją, o tada paleidžia PR diegimo kompiliavimą naudojant blinking_led_pr_bravo.

Ši komanda iš naujo sintezuoja blinking_led_child_slow sintezės versiją, o tada paleidžia PR diegimo kompiliavimą naudojant blinking_led_pr_bravo. - Norėdami atlikti tik sintezės versijų kompiliavimą, paleiskite šią komandą: Ši komanda nekompiliuoja iš naujo pagrindinės versijos.

- Norėdami atlikti diegimo pataisų kompiliavimą, paleiskite šią komandą:

- Ši komanda neperkompiliuoja pagrindinės versijos.

- Norėdami užprogramuoti gautą RBF, atlikite veiksmus, nurodytus 10 veiksme: Plokštės programavimas 22 puslapyje file į FPGA.

Pastaba: Kad nebūtų vykdomas visas kiekvienos peržiūros srautas, scenarijuje setup.tcl apibrėžkite tik sintezei skirtas ir įgyvendinimo versijas ir paleiskite scenarijų.

Naujos asmenybės įtraukimas į dizainą

Visiškai sukūrę bazines versijas, vis tiek galite pridėti naujų asmenybių ir atskirai kompiliuoti šias asmenybes.

Pavyzdžiui,ample, norėdami apibrėžti naują vaiko asmenybę blinking_led_parent_slow, kuri išjungia led_three:

- Nukopijuokite blinking_led_child_empty.sv į blinking_led_chdild_off.sv.

- Blinking_led_child_off.sv file, pakeiskite priskyrimą, priskirkite led_three_on = 1'b0; priskirti led_three_on = 1'b1;. Įsitikinkite, kad pakeitėte modulio pavadinimą iš blinking_led_child_empty į blinking_led_child_off.

- Sukurkite naują sintezės versiją, blinking_led_child_off, atlikdami veiksmus, nurodytus „Tik sintezei skirtų versijų kūrimas“ 16 puslapyje.

Pastaba: Blinking_led_child_off versija turi naudoti blinking_led_child_off.sv file. - Sukurkite naują diegimo versiją blinking_led_pr_foxtrot, atlikdami veiksmus, nurodytus Diegimo pataisų kūrimas 15 puslapyje.

- Atnaujinkite a10_hier_partial_reconfig/setup.tcl file apibrėžti naują PR įgyvendinimą:

- Sukompiliuokite tik šią naują sintezės ir įgyvendinimo peržiūrą vykdydami šią komandą:

Išsamios informacijos apie „Intel Arria 10“ įrenginių hierarchinį dalinį konfigūravimą rasite „Intel Quartus Prime Pro Edition“ vadovo 1 tome dalyje Dalinės perkonfigūracijos dizaino kūrimas.

Susijusi informacija

- Dalinio perkonfigūravimo projekto kūrimas

- Dalinės konfigūracijos internetinis mokymas

Dokumento taisymo istorija

5 lentelė. Dokumento taisymo istorija

| Dokumento versija | Programinės įrangos versija | Pakeitimai |

| 2017.11.06 | 17.1.0 | • Atnaujinta Nuorodų projektavimo reikalavimai skyrių su programinės įrangos versija

• Atnaujinta Plokščias etaloninis dizainas be PR skaidymo figūra su dizaino bloko pakeitimais • Atnaujinta Nuorodų dizainas Files lentelė su informacija apie Top_counter.sv modulis • Atnaujinta Dalinis perkonfigūravimas IP pagrindinio integravimo figūra su dizaino bloko pakeitimais • Atnaujinti skaičiai – Dizaino pertvarų langas ir Loginis užrakto regionų langas kad atspindėtų naują GUI • File pavadinimo pasikeitimai • Teksto redagavimas |

| 2017.05.08 | 17.0.0 | Pirminis dokumento išleidimas |

Dokumentai / Ištekliai

|

intel AN 805 hierarchinė dalinė dizaino perkonfigūracija Arria 10 SoC plėtros plokštėje [pdfVartotojo vadovas AN 805 Hierarchinė dalinė dizaino perkonfigūracija Arria 10 SoC kūrimo plokštėje, AN 805, Hierarchinė dalinė dizaino perkonfigūracija Arria 10 SoC kūrimo plokštėje, Arria 10 SoC plėtros plokštės dizaino perkonfigūracija, Arria 10 SoC plėtros plokštė, 10 SoC Vystymosi taryba |